Product Summary

The EP1800ILC-70 is an EPLD. It offers a solution to high-speed, low power logic integration. Fabricated on advanced CMOS technology, Classic devices also have a Turbo-only version, which is described in this data sheet. The EP1800ILC-70 supports 100% TTL emulation and can easily integrate multiple PAL- and GAL-type devices with densities ranging from 300 to 900 usable gates. The EP1800ILC-70 provides pin-to-pin logic delays as low as 10 ns and counter frequencies as high as 100 MHz. The EP1800ILC-70 is available in a wide range of packages, including ceramic dual in-line package (CerDIP), plastic dual in-line package (PDIP), plastic J-lead chip carrier (PLCC), ceramic J-lead chip carrier (JLCC), pin-grid array (PGA), and small-outline integrated circuit (SOIC) packages.

Parametrics

EP1800ILC-70 absolute maximum ratings: (1)VCC Supply voltage With respect to ground:–2.0V to 7.0V; (2)VI DC input voltage With respect to ground:–2.0V to 7.0V; (3)IMAX DC VCC or ground current: –300 to 300mA; (4)IOUT DC output current, per pin: –25 to 25mA; (5)TSTG Storage temperature No bias:–65℃ to 150℃; (6)TAMB Ambient temperature Under bias :–65℃ to 135℃; (7)TJ Junction temperature Ceramic packages, under bias: 150℃; (8)Plastic packages, under bias: 135℃.

Features

EP1800ILC-70 features: (1)Complete device family with logic densities of 300 to 900 usable gates; (2)Device erasure and reprogramming with non-volatile EPROM configuration elements; (3)Fast pin-to-pin logic delays as low as 10 ns and counter frequencies as high as 100 MHz; (4)24 to 68 pins available in dual in-line package (DIP), plastic J-lead chip carrier (PLCC), pin-grid array (PGA), and small-outline integrated circuit (SOIC) packages; (5)Programmable security bit for protection of proprietary designs; (6)100% generically tested to provide 100% programming yield; (7)Programmable registers providing D, T, JK, and SR flipflops with individual clear and clock controls; (8)Software design support featuring the Altera MAX+PLUS II development system on Windows-based PCs, as well as Sun SPARCstation, HP 9000 Series 700/800, IBM RISC System/6000 workstations, and third-party development systems; (9)Programming support with Altera’s Master Programming Unit (MPU); programming hardware from Data I/O, BP Microsystems, and other third-party programming vendors; (10)Additional design entry and simulation support provided by EDIF, library of parameterized modules (LPM), Verilog HDL, VHDL, and other interfaces to popular EDA tools from manufacturers such as; (13)Cadence, Exemplar Logic, Mentor Graphics, OrCAD, Synopsys, Synplicity, and VeriBest.

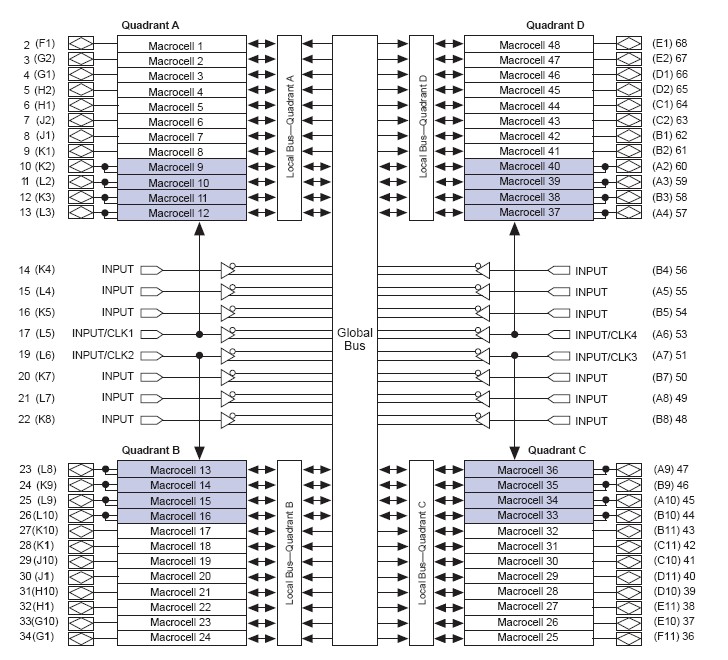

Diagrams

|

EP1800ILC-90 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

EP1800ILI-90 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

EP1800JC-2 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

EP1800JC-3 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

EP1800JM883B |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

EP1810 |

Other |

|

Data Sheet |

Negotiable |

|

||||

(Hong Kong)

(Hong Kong)